# **Evaluating the Memory Performance** of a ccNUMA System

Uroš Prestor

September 5, 2001

#### **Abstract**

Scalable cache-coherent nonuniform memory access (ccNUMA) architectures are an important design segment for high-performance scalable multiprocessor systems. In order to write application programs that take advantage of such systems, or port application programs written for symmetric multiprocessor systems with uniform memory access times, it is important to understand the impact of nonuniform memory access times and the associated ccNUMA cache coherence protocols on aggregate application memory performance. This work presents a detailed memory performance analysis of a particular ccNUMA system (the SGI Origin 2000). The thesis presents a new memory profiling tool, called snperf, and a new set of microbenchmark codes, called snbench, which make such a fine-grained memory performance analysis possible. The analysis was performed on a wide variety of Origin 2000 system configurations and demonstrates that memory locality has a strong impact on application performance. More importantly, the results demonstrate a variety of second-order memory performance effects that are also substantial performance influences. Even though the specific implementation target for this thesis was the Origin 2000 architecture, the methods are applicable to other ccNUMA systems.

# **Contents**

| 1 | Intr | oduction  | ı                                       | 7  |

|---|------|-----------|-----------------------------------------|----|

| 2 | Rela | ited Wor  | ·k                                      | 9  |

|   | 2.1  | Microb    | enchmarks                               | 9  |

|   | 2.2  | Perform   | nance Analysis Tools                    | 12 |

| 3 | Bacl | kground   |                                         | 15 |

|   | 3.1  | Directo   | ry-Based Cache Coherence                | 16 |

|   |      | 3.1.1     | Protocol Operation                      | 17 |

|   |      | 3.1.2     | Directory Organization                  | 18 |

|   |      | 3.1.3     | Performance and Correctness Issues      | 19 |

|   | 3.2  | Origin 2  | 2000 Hardware Design                    | 21 |

|   |      |           | Cache Coherence Protocol                |    |

|   |      | 3.2.2     | Node Board                              | 25 |

|   |      | 3.2.3     | Interconnect Network                    | 29 |

|   |      | 3.2.4     | Physical System Organization            | 31 |

|   | 3.3  |           | Coperating System                       |    |

|   |      |           | Hardware Graph                          |    |

|   |      | 3.3.2     | Distributed Memory Management           | 35 |

| 4 | Arcl | hitectura | al Evaluation of the Origin 2000        | 39 |

|   | 4.1  | Protoco   | ol Transactions and Coherence States    | 40 |

|   |      | 4.1.1     | Composite Cache Coherence State         | 40 |

|   |      |           | Processor Actions and Protocol Requests |    |

|   |      | 4.1.3     | Directory Protocol Transactions         | 43 |

|   | 4.2  |           | h Implementation Overview               |    |

|   |      | 4.2.1     | Measuring Memory Bandwidth              | 47 |

|   |      |           | Measuring Back-to-Back Latency          |    |

|   |      |           | Measuring Restart Latency               |    |

|   | 4.3  |           |                                         |    |

|   |      | 4.3.1     | Local Transactions                      | 54 |

|   |      |           | Remote Transactions                     |    |

|   |      |           | Interventions                           |    |

|   |      | 4.3.4     | Invalidations                           | 68 |

| 5 | The  | ccNUN   | IA Memory Profiler               | 75    |

|---|------|---------|----------------------------------|-------|

|   | 5.1  | ccNUI   | MA Performance Metrics           | . 75  |

|   |      | 5.1.1   | Thread Metrics                   | . 76  |

|   |      | 5.1.2   | Node Metrics                     | . 77  |

|   |      | 5.1.3   | Network Metrics                  | . 78  |

|   | 5.2  | Origin  | Hardware Event Counters          | . 78  |

|   |      | 5.2.1   | MIPS R10000 Performance Counters | . 78  |

|   |      | 5.2.2   | Hub Event Counters               | . 79  |

|   |      | 5.2.3   | Router Histogram Counters        | . 81  |

|   | 5.3  | Implei  | mentation                        | . 81  |

|   |      | 5.3.1   | Loadable Kernel Module           | . 82  |

|   |      | 5.3.2   | System Activity Monitor          | . 87  |

|   |      | 5.3.3   | Application Launcher             | . 91  |

|   |      | 5.3.4   | Post-Mortem Analysis             | . 93  |

| 6 | Exa  | mples   |                                  | 95    |

|   | 6.1  | Memo    | ory and Link Utilization         | . 95  |

|   | 6.2  |         | Effects of Prefetch Instructions |       |

|   | 6.3  | Backo   | ff Transactions                  | . 98  |

|   | 6.4  | SPLA    | SH-2 FFT                         | . 100 |

| 7 | Con  | clusion |                                  | 105   |

| 8 | Ack  | nowled  | gments                           | 108   |

| A | 128- | Process | sor System Results               | 109   |

# **List of Figures**

| 2.1  | The $P^3$ diagram for a 250 MHz Origin system                 | 10 |

|------|---------------------------------------------------------------|----|

| 3.1  | Reducing protocol latency through forwarding                  | 20 |

| 3.2  | Logical organization of the Origin 2000 system                |    |

| 3.3  | Block diagram of the node board                               |    |

| 3.4  | Block diagram of the Hub ASIC                                 | 27 |

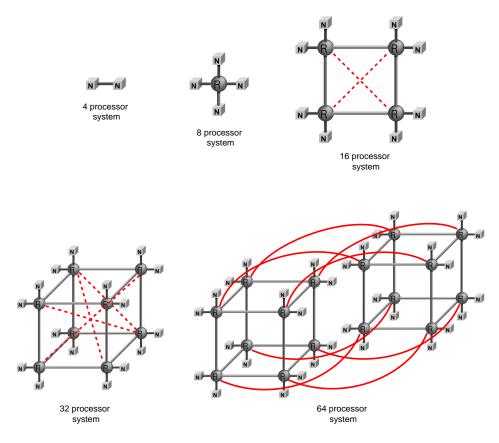

| 3.5  | Origin 2000 topologies from 4 to 64 processors                | 30 |

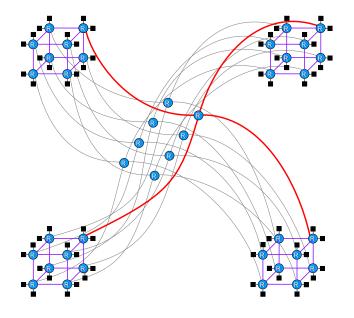

| 3.6  | 128 processor Origin 2000 system topology                     | 30 |

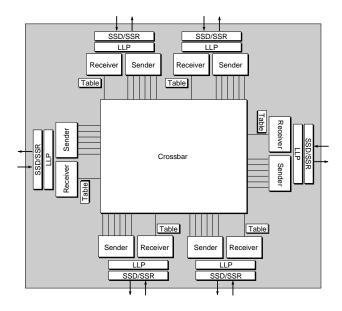

| 3.7  | Block diagram of the Router ASIC                              |    |

| 3.8  | Physical configuration of a 32-processor Origin system        | 33 |

| 3.9  | Physical configuration of a 128-processor Origin system       | 33 |

| 3.10 | Irix memory locality management example                       | 38 |

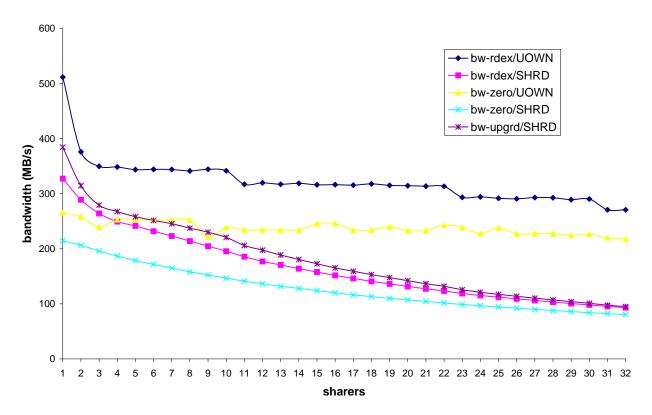

| 4.1  | Directory protocol transactions generated by a RDEX request   | 44 |

| 4.2  | Kernels used in bandwidth experiments                         | 49 |

| 4.3  | Kernels used in back-to-back latency experiments              | 49 |

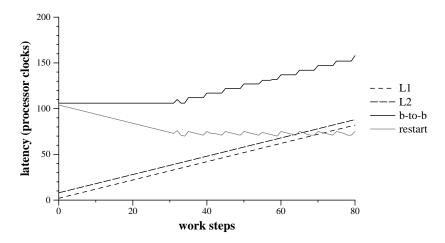

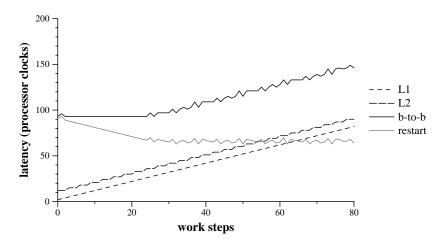

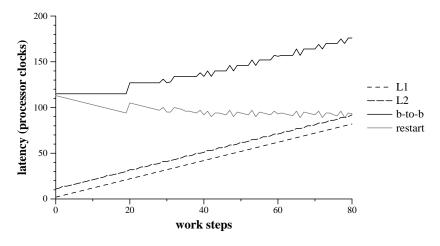

| 4.4  | Back-to-back and restart latencies on a R10K 250/250/4 system | 52 |

| 4.5  | Back-to-back and restart latencies on a R10K 195/130/4 system | 52 |

| 4.6  | Back-to-back and restart latencies on a R12K 300/200/8 system | 52 |

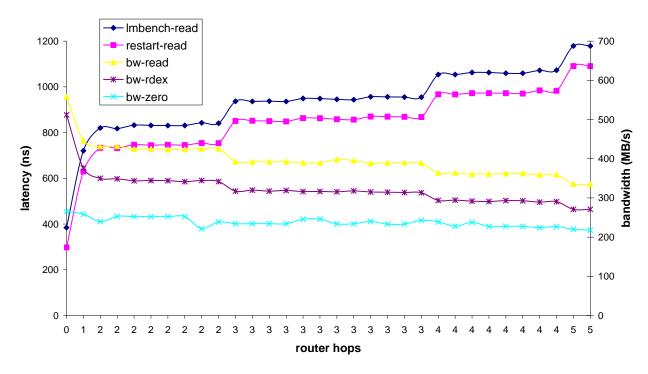

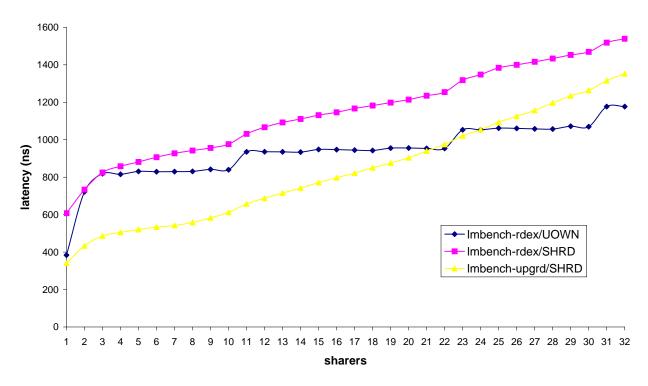

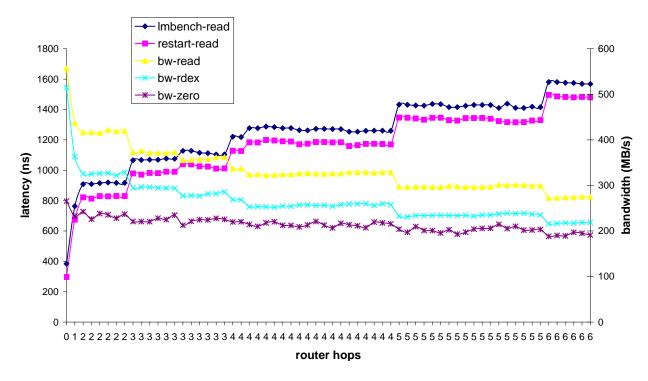

| 4.7  | Remote latency and bandwidth chart                            | 62 |

| 4.8  | Message flow in unowned transactions                          | 62 |

| 4.9  | Message flow in clean-exclusive transactions                  | 64 |

| 4.10 |                                                               |    |

| 4.11 | Message flow in invalidate experiments                        |    |

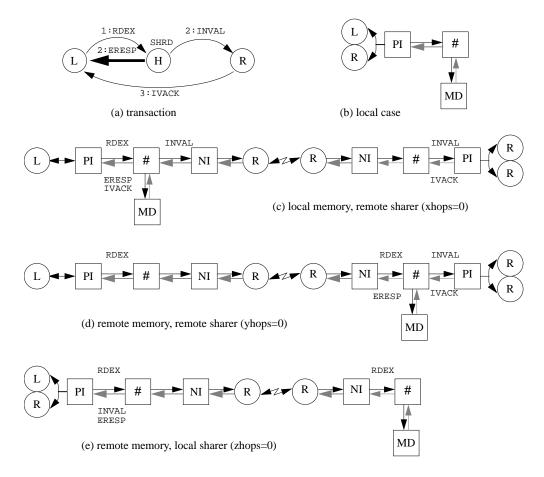

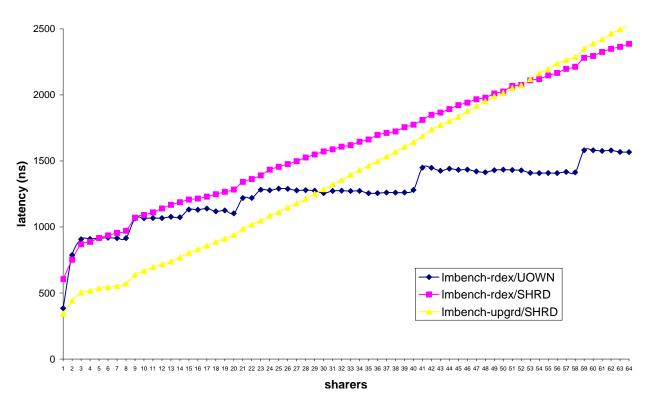

| 4.12 | Invalidate latency chart                                      | 71 |

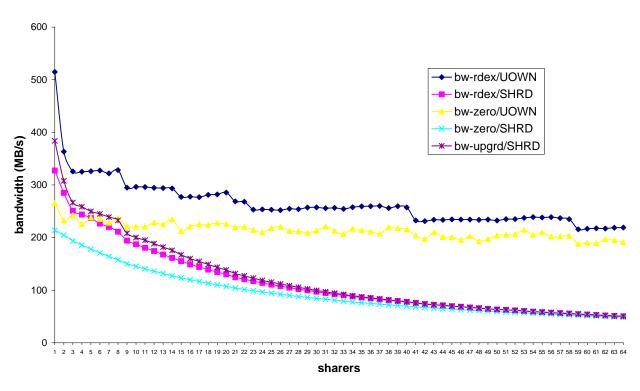

|      | Invalidate bandwidth chart                                    |    |

| 4.14 | Single sharer message flow                                    | 73 |

| 5.1  | Sample code fragment opening and initializing a Hub MD device | 85 |

| 5.2  | Sample code fragment opening and initializing a link device   | 86 |

| 5.3  | Sample invocation of snsar                                    | 88 |

| 5.4  | Sample invocation of snrun                                    | 91 |

| 5.5  | Sample output from sninfo                                     |    |

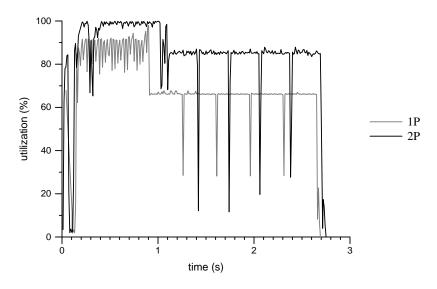

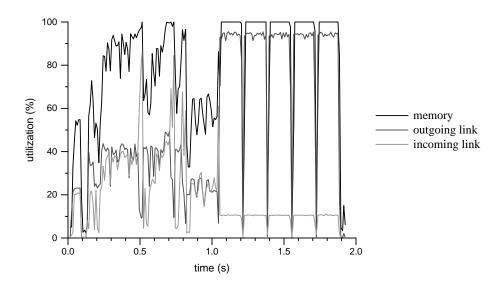

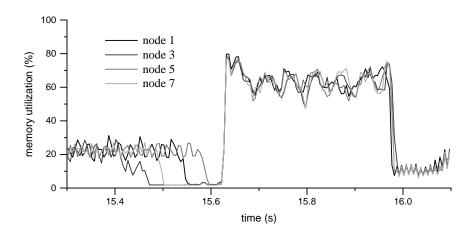

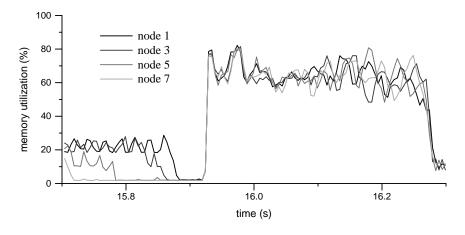

| 6.1  | Memory utilization for 1- and 2-thread local reduction loop   |    |

| 6.2  | A comparison of memory and link utilizations                  | 97 |

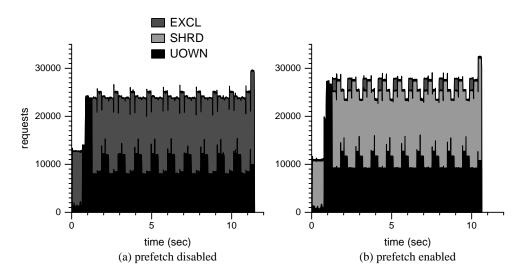

| 6.3         | STREAM directory state breakdown                        |

|-------------|---------------------------------------------------------|

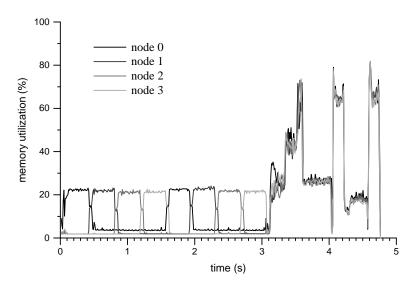

| 6.4         | FFT memory utilization profile on four nodes            |

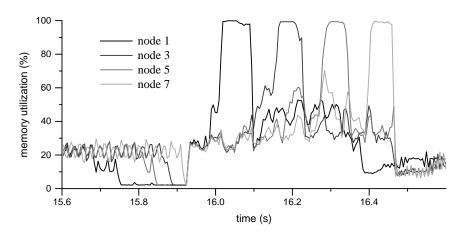

| 6.5         | Unoptimized FFT matrix transpose without staggering     |

| 6.6         | FFT matrix transpose with basic staggering              |

| 6.7         | FFT matrix transpose with optimized staggering          |

| <b>A</b> .1 | 128-processor system remote latency and bandwidth chart |

| A.2         | 128-processor system intervention latency chart         |

| A.3         | 128-processor system intervention bandwidth chart       |

# **List of Tables**

| 3.1  | Directory states in the Origin directory protocol                    | .3 |

|------|----------------------------------------------------------------------|----|

| 4.1  | Snbench composite cache coherence states                             | -1 |

| 4.2  | Processor actions and protocol requests                              | 2  |

| 4.3  | Memory bandwidth experiments                                         | .7 |

| 4.4  | Back-to-back memory latency experiments                              | 8  |

| 4.5  | Origin 2000 systems used in experiments                              | 4  |

| 4.6  | Local results for a R10K 195/130/4 system                            | 5  |

| 4.7  | Local results for a R10K 250/250/4 system                            | 7  |

| 4.8  | Local results for a R12K 300/200/8 system                            | 7  |

| 4.9  | Local results for a R12K 400/266/8 system                            | 7  |

| 4.10 | A comparison of local results                                        | 8  |

| 4.11 | Remote results on a 64P Origin R12K 300/200/8                        | 9  |

| 4.12 | Remote results on a 128P Origin R12K 300/200/8                       | 9  |

| 4.13 | Remote results for a 64P R12K 300/200/8 system 6                     | 1  |

| 4.14 | Remote penalty and average router delays                             | 3  |

| 4.15 | Remote latencies for clean-exclusive miss transactions 6             | 5  |

| 4.16 | Remote latencies for clean-exclusive hit transactions                | 6  |

| 4.17 | Remote latencies for dirty-exclusive transfer (DEXT) transactions 6  | 7  |

| 4.18 | Remote latencies for dirty-exclusive downgrade (DEXD) transactions 6 | 8  |

| 4.19 | Invalidate results for a 64P R12K 300/200/8 system                   | 0  |

| 4.20 | Remote latencies for single-sharer invalidations                     | 4  |

| 5.1  | R10000 performance counter events                                    | 9  |

| 5.2  | Hub Memory/Directory event counting modes                            | 0  |

| 5.3  | Hub IO event counter definitions                                     | 0  |

| 5.4  | Router histogram counter registers                                   | 1  |

| 5.5  | Device files created by the LKM                                      | 3  |

| 5.6  | The ioctl commands defined by the LKM                                | 3  |

| 5.7  | Device files in the extended LKM interface                           | 7  |

| 5.8  | Options recognized by the system activity monitor                    | 8  |

| 6.1  | Aggregate memory bandwidth for backoff invalidates                   | 9  |

| A.1  | Remote and intervention results for a 128P system                    | 0  |

# **Chapter 1**

# Introduction

Among scalable multiprocessor systems, cache-coherent nonuniform memory access (ccNUMA) designs are becoming increasingly popular. Compared to the traditional shared-bus (SMP) systems, they scale to much higher processor counts because their scalability is not limited by a single shared resource. Compared to other scalable multiprocessor designs, they are much easier to program. Like SMP systems, ccNUMA systems implement a globally coherent, shared address space in hardware. The applications written for SMP systems do not require any changes in order to execute on ccNUMA systems, an important consideration when existing codes are to be migrated on new architectures.

However, scalability does not come without cost. While the applications written for a SMP system run unmodified on a ccNUMA system, new factors need to be considered when tuning application performance. Just like other scalable multiprocessors, ccNUMA designs replace one shared resource (system bus) with a collection of distributed resources and any one of them can become a performance bottleneck. More importantly, the basic memory performance characteristics (latency and bandwidth) change depending on where the memory is allocated. On SMP systems, the cost of a memory access is constant for all processors and all memory locations in the system. On ccNUMA systems, the cost of a memory access depends on data placement and on the type of the coherency transaction. Even in the most aggressive implementations of a ccNUMA architecture, the cost of a remote memory access is more than twice the cost of a local memory access.

On SMP systems, the performance analysis of parallel programs needs to address (among other things) application cache behavior, load balancing, and the undesired artifacts of the cached, shared address space (e.g., false sharing). On ccNUMA systems, performance analysis also needs to address application memory behavior. While there are ccNUMA systems which offer operating system support for achieving memory locality, the automated features are not always sufficient. Applications typically need to carefuly tune their data placement in order to achieve good performance on ccNUMA architectures. The research on performance analysis for uniprocessor and SMP systems has produced a variety of methods and tools. When analyzing memory performance, these tools may distinguish between a cache hit or a miss, and they may even be aware of the cache hierarchy. However, very few tools focus on application memory behavior, especially in a nonuniform memory access environment. Furthermore, even though the implementations of the ccNUMA architecture have been available commercially for a number of years, there is no comprehensive study that evaluates the system performance in order to find the secondary effects of

ccNUMA architectures on application performance.

The SGI Origin 2000 system is an aggressive implementation of a ccNUMA architecture. The system scales from two to 512 processors, the operating system includes extensive support for NUMA programming and there is a rich set of tools for parallel program development. The system includes hardware support for performance analysis: both the processor and various system ASICs include a set of hardware event counters that can be used for application profiling. SGI offers a set of performance analysis tools that use processor event counters for application profiling [43, 51]. Even though the hardware event counters in the Hub and Router ASICs offer valuable information about the application memory behavior, the directory cache coherence transactions, and the interconnect network traffic, there are no tools that use this information to aid in performance analysis of parallel programs on the Origin. Furthermore, very little information exists about the memory system performance of large Origin systems. The existing publications [19, 50] focus on small systems, and they do not evaluate the impact of the directory protocol on memory performance.

The contribution of this thesis is twofold. First, it gives a detailed analysis of the memory performance on the Origin 2000, evaluating the system architecture, the directory cache coherence protocol, and the trade-offs that influenced their design. Second, it presents a way of analyzing application memory performance using the information provided by the Origin hardware event counters. A suite of microbenchmarks, snbench, was written to help evaluate Origin memory performance and the directory protocol. The microbenchmarks measure memory latency and bandwidth for different directory protocol transactions, and various combinations of thread and memory placements. The snbench suite was used to analyze a number of Origin systems, from the early 195 MHz R10000 systems to the latest 400 MHz R12000 systems, and ranging in size from dual-processor to 128-processor systems. A memory profiling tool, snperf, uses the information provided by the Origin hardware event counters to evaluate application memory behavior. The profiler continuously samples the event counters for the duration of the application execution and stores the samples into a trace file. The post-mortem analysis tool uses the high-precision timestamps in the trace files to correlate events in application threads, the memory system and the network interface. Combined thread, node and network metrics present a picture of the application resource usage, which may reveal potential performance problems. The Irix operating system does not provide an interface to the hardware event counters that supports high-resolution (sub 1 ms) sampling. Since one of the goals of the memory profiler was to capture the behavior in short application phases (e.g., the matrix transpose in the FFT kernel), a new interface to the hardware event counters was needed. The snpc loadable kernel module (LKM) exports the hardware event counters as a set of memory mapped files, enabling the profiler to be written as a regular user process, which increases the flexibility of the profiler and minimizes the impact on the operating system. Even though the microbenehmark suite and the memory profiler were written for the Origin 2000, we believe that our approach is applicable to other ccNUMA systems.

The thesis is organized as follows: Chapter 2 discusses related work. Chapter 3 introduces the basic concepts behind the directory-based cache coherence, and gives an overview of the Origin 2000 hardware implementation and the ccNUMA features of the Irix operating system. Chapter 4 presents the implementation of the snbench microbenchmark suite, and the results collected on a variety of Origin systems. The implementation of the memory profiler and the loadable kernel module is presented in Chapter 5, while Chapter 6 shows some examples of how the memory profiler can be used. Chapter 7 concludes the thesis.

# Chapter 2

# **Related Work**

#### 2.1 Microbenchmarks

Microbenchmarks are small programs designed to measure a very specific aspect of an underlying system architecture. Microbenchmarks can be written in assembly or in a high-level language. In the later case, they evaluate not just the hardware performance but also the quality of the compiler and the supporting run-time libraries. The results from a collection of microbenchmarks can be used to predict performance of more complex applications.

One of the pioneering works in using micro benchmarks to evaluate system characteristics was done by R. Saavedra [33, 34, 35]. His collection of microbenchmarks evaluates both CPU and memory performance. The CPU microbenchmarks are defined in terms of an abstract machine that is essentially a Fortran execution environment. Most of the CPU metrics are based on arithmetic and trigonometric functions: integer and floating-point add, multiply and divide, complex arithmetic, intrinsic functions, logical operations, branch/switch operations, procedure calls, array indexing, and loop overhead. Saavedra also introduced a novel way of evaluating memory performance. He uses two computing kernels to stride through arrays of different sizes. The *readuse kernel* (RU) is used to measure memory read performance; this is a simple reduction sum. The *read-modify-write kernel* (RMW) combines read and write operations. For example, a RMW kernel for a given array size R and stride S is:

```

for (i=0; i < R; i += S)

a[i] = a[i]*a[i] - CONST;

```

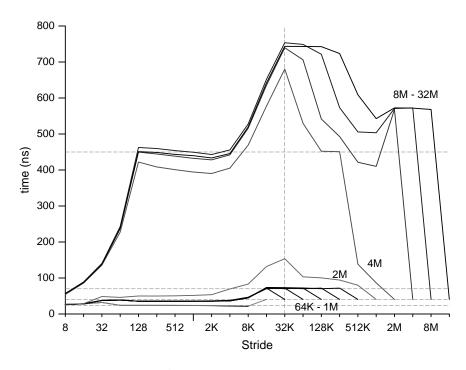

The  $P^3$  diagram is constructed by varying the array size R and stride S. This process yields a number of curves, where each curve represents a fixed array size and the data points on each curve give timing results for a given array stride (increasing in powers of two). Figure 2.1 shows the  $P^3$  diagram for a RMW kernel measured on a 250 MHz Origin. The array size varies from 16 KB to 32 MB.

The  $P^3$  diagrams reveal various levels of the memory hierarchy and the latency characteristics of each memory level. Memory parameters can be deduced by observing when the plots move between different regimes. Saavedra [33] has shown how to use the  $P^3$  diagrams to infer block size, cache size, associativity and even the fact that replacement strategy is random instead of LRU or FIFO. For example, Figure 2.1 reveals that the primary data cache size is 16K (the 16 KB curve

Figure 2.1: The  $P^3$  diagram for a 250 MHz Origin system

fits entirely in L1). The secondary cache size is 4 MB two-way set-associative with a random replacement policy: all curves up to and including 1 MB fit in the L2; the 2 MB curve is slightly above others which implies that the set size is 2 MB with a random replacement algorithm (some lines are replaced even though the whole array fits in one cache set); there are two sets in the cache because the 4 MB curve is just slightly below the curves for larger array sizes where each miss goes to main memory (again, the curve is slightly lower due to random replacement). The secondary cache is not truly set-associative: it uses way prediction bits that are revealed by increased latency for 64 KB – 1 MB cirves at strides 16–512 KB. A miss to main memory combined with a writeback of a dirty line costs  $\approx 450$  ns; the secondary cache line size is 128 bytes (curves 4M–32M flatten out at stride 128). Each TLB entry maps two consecutive 16 KB pages and the TLB miss penalty is  $\approx 300$  ns (the jump for 4M+ curves when stride exceeds 32 KB).

While the  $P^3$  diagrams reveal the basic memory parameters, the measured latencies do not accurately reflect the memory timing. There are several reasons for the inaccuracies. First, the RU and RMW kernels do not use dependent loads—an optimizing compiler will unroll the loop several times and issue the loads in parallel; the measured time of the kernel, divided by the number of loads therefore reflects the *pipelined load latency*, where multiple loads can overlap on a processor capable of processing more than one outstanding load. Second, the microbenchmark includes the loop overhead, and it makes no attempt to subtract it from the total time. Third, the loop is timed with standard Unix time functions; the precision of such timer facilities is usually around 10 ms, which requires a high number of repetitions for accurate results.

Another collection of microbenchmarks which evaluates memory parameters is Imbench [28] by McVoy and Staelin. Unlike Saavedra's microbenchmarks, which focus on the CPU performance, McVoy and Staelin's microbenchmarks were designed to evaluate operating system per-

formance. They include codes which measure the time for process context switching, interprocess communication, I/O, virtual memory system performance, and various Unix system calls (e.g., fork, exec and getpid). The lmbench suite of tests also includes two microbenchmarks that evaluate memory latency and bandwidth parameters. They recognize the deficiency of Saavedra's kernels to evaluate memory latency; instead of the pipelined latency they measure latency by timing the execution of a pointer-chasing loop (p = p). (Early versions of this benchmark also assumed that the load instruction takes one clock cycle and thus subtracted one clock cycle from the measured latency). Similar to Saavedra's  $P^3$  diagrams, their latency microbenchmark varies the size of the linked pointer list and the stride between the elements. The resulting latency plots are similar to Saavedra's  $P^3$  diagrams.

The latency measurement in Imbench is quite accurate given that the microbenchmark is portable and written in a high-level language (C). McVoy and Staelin's method has some problems, though. For example, they assume that the cache has a LRU replacement policy—a walk through an array larger than the cache does result in a few cache hits on systems with a random replacement policy but the number of hits is comparatively small and does not significantly skew the results. Additionally, the pointer-chasing kernel measures the *back-to-back latency*, which is a pessimistic estimate of memory latency. On systems that return the critical data word first, the back-to-back latency includes the time when the processor is blocked due to a shared resource (e.g., the secondary cache interface on R10000). McVoy and Staelin argue that the optimistic latency measure (the time from the detection of a miss until the memory returns the critical word and the processor restarts the pipeline which they call latency in-isolation) is too optimistic and not likely to be relevant for actual commercial programs.

Accurately estimating the lower bound on load latency is a nontrivial task, especially when the microbenchmark is intended to be portable. Hristea et al. [19] have written another collection of microbenchmarks that focuses entirely on memory performance. They distinguish between the back-to-back latency (pointer-chasing kernel, similar to the one used by lmbench) and restart latency (i.e., latency in isolation). They estimate the restart latency by adding an increasing amount of work instructions following the load, where the work instructions do not generate any memory requests and are dependent on the result of the load. When the time needed to execute the work instructions exceeds the time when the shared resources are busy, the work time is subtracted from the total time, which yields an estimate of the restart latency. They have compared results on the Origin 2000 and Sun UE 10000. The latency results show a significant difference between the back-to-back and restart times for the R10000. Hristea et al. also recognized that different cachecoherence transactions incur different costs. They use remote threads whose task is to place the cache lines in the desired state. For the Origin, results are presented for unowned, clean-exclusive and dirty-exclusive lines. Finally, Hristea et al. used the microbenchmarks to evaluate NUMA latencies and bandwidths—they present results on the Origin 2000 where the requestor is both at the home node and one hop away.

A popular microbenchmark which evaluates pipelined memory bandwidth is STREAM [27]. The kernels in this microbenchmark use four typical operations used by scientific codes written in Fortran: copying an array to another array, multiplying all elements of an array by a fixed value, computing a sum of two arrays, and computing a sum of two arrays where the second array is multiplied by a scalar. The results are computed on arrays that do not fit in the processor's caches. In all kernels the results are written to a separate array. STREAM does not evaluate pure memory read bandwidth. Both lmbench and Hristea et al. use a reduction loop to evaluate memory

read bandwidth. Additionally, lmbench also evaluates memory write and copy bandwidths by measuring the performance of manually unrolled loops and the library bcopy function.

Our collection of microbenchmarks, called snbench, focuses on back-to-back and restart latencies and memory bandwidth. The primary goal was accuracy instead of portability. The latency kernels were written in assembly to have full control over instruction execution. Another goal of our mucrobenchmarks was the evaluation of ccNUMA coherence protocol transactions: snbench has the ability to place threads and memories anywhere in the system, and to place cache lines in any coherence state before executing the timed kernel. We also use front-end scripts to determine the topology of the Origin system and generate a number of invocations of the snbench executable with different combinations of thread placement. These experiment groups are designed to evaluate the characteristics of several important classes of Origin coherence protocol transactions. We use a pointer-chasing kernel similar to the one used in Imbench to evaluate the back-to-back latency. We have developed a new algorithm to automatically evaluate the restart latency. The basic approach is similar to the one used by Hristea et al., except that our algorithm uses automatically generated kernels in assembly language to get around compiler optimizations. Finally, we use a different algorithm for computing restart latency.

## 2.2 Performance Analysis Tools

Many tools have been used to help users to speed up applications. There are many performance analysis tools and many ways to evaluate program behavior. The most basic information about program execution is the number of times each instruction, statement, basic block, or function has been executed. This information can be collected by instrumenting the executable at either compile or run time. While counts give information about relative frequency of execution for each part of the program, these frequencies do not necessarily have a strong relationship with the time spent in each section. The simplest approach in collecting timing information is to use statistical profiling: the program is interrupted at specified intervals, and the value of the program counter is used to index into an array of counters that can be mapped back into program source code. On Unix systems, the prof command [4] uses this approach.

Statistical profiling can be combined with a static program call graphs to attribute parts of the execution time for each function to the other functions it calls (function's descendants in the call graph). The <code>gprof</code> execution profiler [15] uses instrumentation added by the compiler to obtain runtime information about function call counts. The run-time library also constructs the histogram of the location of the program counter with the help of the operating system. Function call counts and a program counter histogram are combined in a postprocessing step that attributes the time for each function to the functions that call it. Each parent in the call graph receives some fraction of a child's time. With <code>gprof</code>, timing attribution is based on the number of calls from parent to child: if a parent called a child function p times and the child was called p times in all, a fraction of p/p of the total time spent in the child will be attributed to the parent. This does not necessarily reflect true run-time behavior: if calls from function A cause function C to return immediately while calls from function B account for the majority of time spent in C, the attribution of C's time to A and B based only on the number of calls can be inaccurate.

Statistical profiling answers the question about how much time was spent in each part of the program, but it does not give any answers about the cause. The operating system usually collects

some statistics during program execution, such as the number of page faults, floating point exceptions and process memory usage. An integrated performance analysis framework such as SGI's SpeedShop [51] uses this information to help the user characterize program behavior: whether the process is CPU-bound, I/O-bound, or memory-bound. It can also help in program debugging by instrumenting calls to memory allocation functions and matching memory request and release calls. Performance analysis with SpeedShop is done by first profiling the application with one or more experiments and then analyzing the profiles with a separate GUI interface. SpeedShop experiments include both traditional (flat) and call-graph based statistical profiling; in the latter, SpeedShop performs proper attribution of the time spent in the callee to the callers by unwinding the stack on each clock tick to obtain the complete run-time call chain.

With the increasing use of superscalar and out-of order instruction scheduling, it is even more difficult to determine how the program spends its time. However, it is increasingly common for the designers of microprocessors to include hardware support for counting various types of events or even profiling instructions during the execution in processor's pipelines. The MIPS R10000 provided a set of on-chip event counters [48], which can be used to count the number of cache misses, memory coherence operations, branch mispredictions, TLB misses, and to determine instruction mix for both issued and retired instructions (R10000 uses speculative execution along predicted branch paths). Similar hardware performance counters have appeared in other processors: Cray vector processors [10], DEC Alpha [12], HP PA-8000 [20] and Intel Pentium processors.

These counters were primarily used by hardware developers and a few performance analysts. To be used effectively, hardware event counters require some operating system support and tools which use them. Cray Research traditionally offered strong support for hardware performance monitors. SGI was the first workstation and server vendor to include OS support and tools to use hardware performance counters. The Irix operating system supports virtualized performance counters, which are a part of each kernel-visible thread context [44]. Even though the R10000 processor only includes two physical counters, the operating system removes this limitation by multiplexing several events on one hardware counter. No special instrumentation is required to profile a program with hardware event counters. Users can measure cumulative event counts for the whole duration of the process with the perfex tool [43]. SpeedShop uses hardware event counters for statistical profiling by using performance counter overflow as the interrupt source. This makes it possible to correlate processor events (e.g., cache misses) with the locations in program source code.

DEC's Digital Continuous Profiling Infrastructure (DCPI) project [2] used hardware event counters to perform statistical profiling of the entire operating system, including the kernel, shared libraries, and all user-level applications. The data collection was designed for minimal system impact. The DCPI tools provided profile information at varying levels of granularity, from whole images (executables and shared libraries); down to procedures and basic blocks; down to detailed information about individual instructions, including information about dynamic behavior such as cache misses, branch mispredicts, and other stalls. The profiler ran on in-order DEC Alpha processors, which enabled the analysis tools to attribute stalls precisely to each instruction. Precise attribution of instruction stalls is no longer possible on an out-of-order processor. In order to achieve the same level of precision on an out-of-order processor, the DCPI authors designed a new form of hardware support for instruction-level information to be used with the DCPI tools [11]. They proposed an approach where the processor instruction fetch unit selects an instruction in the input stream at random and tags it with a special bit (the *ProfileMe* bit). As a tagged instruction

moves through the processesor pipeline, a detailed record of all interesting events and pipeline stage latencies is collected. This information is made available to the profiling software when the instruction is retired.

With the widespread availability of performance monitoring features in modern microprocessors there is a need to standardize the programming interfaces which are used to access these features. The PerfAPI [29] and PCL [5] projects aim to provide a portable library of functions and a standard set of performance monitoring events to be used by application writers who wish to instrument their codes in a portable way. Both projects support the majority of modern microprocessors and operating systems where the counting of hardware events is possible. They offer different language bindings (C, Fortran, Java) and they define a common set of event definitions; however, not all events may be implemented on all systems, which presents the fundamental problem for portability. The applications that need to be truly portable need to restrict the use of hardware events to the small group which is implemented on all systems (typically the number of CPU cycles and cache misses).

All projects described so far that use hardware event counters look at the application behavior from a processor-centric perspective. They all use performance-monitoring features that are implemented in the processor; while this offers plenty of data about processor-related events, all the information is lost when memory requests leaves the processor. At best, the processor event counters provide the latency of a memory operation and a glimpse into the cache coherence protocol for first- and second-level caches that are typically controlled by the processor. While this information is reflected in the program timings, the performance analyst typically cannot determine application memory behavior, especially in distributed systems with many independent resources (memory controllers, I/O units, network interconnect links) and complex cache coherence protocols. In such systems, distributed resources can become distributed bottlenecks.

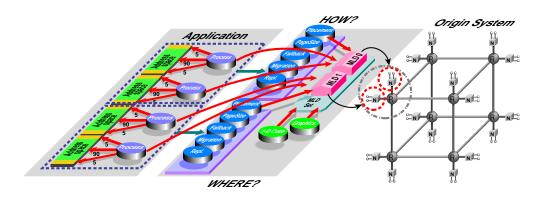

Our memory profiling tool attempts to correlate processor events (thread metrics) with events in the memory subsystem on each node (node metrics) and the interconnect network (network metrics). The memory profiler does not use statistical sampling: to facilitate correlation between various sources of performance data the memory profiler continuously stores samples from processor, node and router counters into a set of output files; each sample is timestamped with a high-resolution clock. The post-mortem analysis tools correlate samples from different trace files and present all metrics on an unified timeline.

# Chapter 3

# **Background**

Multiprocessor systems have been used for a long time to construct computers with a much higher aggregate performance than the fastest uniprocessor system. In order to leverage the fast design cycle of modern microprocessors, the most common way to harness the power of multiple commodity microprocessors is a design based on a common bus that connects the microprocessors, the system memory, and one or more I/O bridges. Such systems use bus snooping to enforce cache coherence; they are commonly referred to as *symmetric multiprocessor systems* (SMPs). This acronym is used in operating system literature to describe multiprocessor kernels where all processors are functionally equivalent, and it is also used by computer architects to describe systems that implement the *shared memory programming* model. In such systems, all processors share the same (physical) address space and the communication is based on memory operations such as loads and stores. The SMP systems typically have support for atomic memory operations, which are the basis of higher level synchronization primitives such as locks, semaphores and barriers. The terms shared memory programming and *uniform memory access* (UMA) are often used interchangeably, although the terms are not strictly equivalent.

SMP systems are widely used as servers and are being used as high-end workstations. They are relatively easy to build and relatively easy to program: the shared address space programming model is well understood. The snoopy bus that is the basis of cache coherence protocols is at the same time the fundamental limitation to their scalability. There are several mechanisms which facilitate a higher bus throughput and thus a higher processor count: multiple interleaved split-transaction busses combined with relaxed memory models and a lot of clever engineering have pushed the number of microprocessors in a single SMP system up to 64. However, such large processor counts are pushing the scalability limits of SMP systems.

Scalable multiprocessors replace a shared bus with a scalable interconnect. This change opens up a vast design space that covers a range of systems from tightly coupled multiprocessor systems to networks of workstations. The shared address space that makes SMP systems so attractive is typically the first casualty of scalability. Scalable multiprocessors replace it with some form of message passing, either explicitly through communication libraries (such as PVM or MPI) or implicitly with parallel language constructs which are translated into messages by the compiler (e.g., High Performance Fortran or OpenMP). The programming model is suitable for relatively coarse-grained parallelism, depending on how tightly the processor is integrated with the network. Clusters of relatively inexpensive computers connected with a fast general-purpose network (Myrinet, 100 MB/s Ethernet) are gaining popularity in scientific processing space due to their

price/performance characteristics. When used with commercial applications, they are typically found in high-availability cluster setups.

However, eliminating the shared bus does not preclude a shared address space. Scalable cache coherence can be implemented with a protocol which keeps track of the state of each cache line by exchanging messages among the participants (processors and memories). Scalable cache coherent systems consist of a number of nodes, each with one or more processors, a portion of system memory and a communication interface; the nodes are linked together with a scalable interconnect. Such systems deliver the convenience of programming in a shared address space and a promise of scalability to high processor counts.

The SGI Origin 2000, although not the first commercially available scalable multiprocessor system, was nonetheless one of the most ambitious designs when it was introduced in the market. Its design came out of two research efforts at Stanford University, the DASH multiprocessor [23] and its follow-on, the FLASH project [22]. Both projects explored the limits of a particular multiprocessor design, the cache-coherent nonuniform memory architecture. The Origin 2000 family of multiprocessor systems was introduced by SGI in 1996. The modular design allows for scalability from two to 512 processors. The hardware cache coherence is achieved by means of a memory-based directory cache coherence protocol. It features an aggressive communication mechanisms and hardware and software support for NUMA features such as page migration and replication, support for explicit thread and data placement and a novel way of enforcing TLB coherence (directory poisoning).

This chapter describes the basics of scalable shared-memory multiprocessing and the design and implementation details of the Origin 2000. Section 3.1 gives an overview of directory-based cache coherence and some of the design trade-offs. In Section 3.2, we describe the choices made by the Origin designers. In particular, we describe the hardware organization, the network topology, and the design of the directory cache coherence protocol. The ccNUMA hardware features need software support. Section 3.3 gives an overview of the operating system interfaces and commands that let user applications take advantage of various Origin hardware features.

### 3.1 Directory-Based Cache Coherence

The cache coherence in SMP systems is typically enforced with a snoopy bus protocol such as MESI (Illinois) [30]. The unit of coherence is a small cache line (usually between 32 and 128 bytes). Each processor maintains a state of each cache line in its local cache, In the MESI protocol, the state is either invalid, shared, exclusive or modified. Several processors may have a read-only copy of a shared cache line in their local caches simultaneously. A processor can obtain an exclusive copy, which requires that the other processors invalidate that cache line in their local caches. A processor can modify the contents of a cache line only after obtaining exclusive ownership; at that time, the state is changed from exclusive to modified. When the line is in the modified state, the current owner will supply the data when another processor requests a copy. The data for exclusive lines can be supplied either by the owner or by the memory controller. The cache controller performs state transitions by processing memory requests from the processor and by snooping on the requests on the shared bus. The simplicity of this scheme relies on the shared bus. All memory requests are broadcast on the bus and all processors (and memory controllers) listen in on the traffic.

A scalable multiprocessor decouples the system into a set of nodes linked together with a scalable interconnection network. Each node consists of one or more processors with corresponding caches, a portion of system memory, and a communication assist which connects the node to the rest of the system. There are several approaches to achieving cache coherence in scalable multiprocessors. The broadcast and snooping mechanism can be extended with a hierarchy of broadcast media such as busses or rings. Another approach is based on the concept of a directory: the global state of each cache line is maintained in a known location—the directory—where the requests can go and look it up. Each cache line is assigned a home where the directory state is kept. Typically, each node in the system is home to a portion of the system memory. Yet another approach uses a two-level protocol hierarchy where the inner protocol keeps the data coherent within a node and the outer protocol maintains global coherence. The inner and outer protocols need not be the same. A common organization is for the outer protocol to be a directory protocol and the inner one to be a snooping protocol [23, 25]. Other combinations, such as snooping-snooping [13] and directory-directory [9] are also possible.

On a machine with physically distributed memory, nonlocal data may be replicated either in the processor's caches or in the local main memory. The systems that replicate data only in processor caches and keep the data coherent in hardware at the granularity of cache lines similar to the bus-based systems are called *cache-coherent nonuniform memory access* (*ccNUMA*) architectures. More generally, systems that provide a shared address space programming model with physically distributed memory and coherent replication (either in caches or in local memory) are called *distributed shared memory* (*DSM*) systems. The ccNUMA approach is an example of the DSM architecture. Other DSM system architectures include COMA (cache-only memory architecture) [13, 18], Simple COMA [36, 32], and software DSM approaches [24, 6, 21]. The design space for DSM architectures is very broad; however, performance issues favor designs which implement cache coherence in hardware. Among hardware solutions, directory-based ccNUMA systems appear to be the most popular choice for scalable shared-memory multiprocessing.

### 3.1.1 Protocol Operation

The directory protocol is invoked if the processor makes an access that its cache cannot satisfy by itself. For example, an access to a cache line which is not present in processor's cache or a store to a read-only copy of the cache line. Unlike the snoopy cache coherence where the processor simply places the request on the shared bus and waits for a response from either memory or another processor, the directory protocol has to communicate with other participants in the system in order to satisfy the request. First, the protocol needs to find out enough information about the state of the cache line to determine what action to take. If there are other copies cached in the system, the protocol must be able to locate them in case it needs to invalidate them. Finally, the protocol must provide a way of communicating with the other copies. The directory protocol finds the information about the state of cache lines by looking up the directory through network transactions. The location of copies is also found from the directory and the communication with other copies is done by network transactions in an arbitrary interconnection network.

In a ccNUMA system, each cache line is assigned a *home node*. The home keeps the global state of the cache line in addition to the data. Each node in the system is home to a portion of total system memory; the home node is determined from the globally unique address of the cache line. The nodes are connected in a network. In addition to the memory controler, each node also has a

communication assist which is responsible for communicating with other nodes. The *local node*, or *requesting node* is the node containing the processor that issues a request for the cache line. The communication assist in the local node sends a network message to the home node asking for a copy of the cache line. Depending on the directory state of the cache line, the protocol returns a copy immediately if there are no other copies cached in the system. If there are read-only copies cached by other nodes in the system and the local node requests an exclusive copy, the directory needs to locate all *sharer nodes* and invalidate their copies before granting the local node exclusive access. Finally, if the only valid copy of the cache line is located in a remote processor's cache, the directory needs to locate the *dirty node*, invalidate the dirty copy in remote processor's cache and send the modified data to the local node (SGI literature refers to this as an *intervention*). The *owner node* is the node that currently holds a valid copy of the cache line and must supply data when needed; in directory protocols, the owner is either the home node or the dirty node.

When a cache miss occurs, the local node sends a request to the home node where the directory information for the cache block is located. On a read miss, the directory indicates from which node the data may be obtained; on a write miss, the directory identifies the copies of the block and the protocol needs to invalidate the copies by sending invalidate messages to each individual copy. Each invalidation requires a separate acknowledgment after the node has invalidated the cache line in its processor's caches; in systems which implement strict memory consistency (such as Origin 2000), the local node can proceed with a write only after the acknowledgments from all sharer nodes have been received.

### 3.1.2 Directory Organization

The natural place for directory information is to include it with the main memory in the home node. At the very least, the directory information needs to include cache line state and enough information to locate the owner or the list of sharers. This scheme is known as flat directory scheme because the source of directory information is determined by the address of the cache line. On a cache miss, a single network transaction is sent directly to the home node to look up the directory regardless of how far the home node is. An alternative to the flat memory scheme is to organize the directory as a hierarchical data structure (a tree). In the *hierarchical directory schemes*, the source of directory information is not known a priori: upon a miss, the directory information is found by traversing up the hierarchy by network transactions until a node is reached which indicates that its subtree has the desired information. The latency and bandwidth characteristics of hierarchical directory schemes tend to be much worse than that of the flat schemes; hierarchical organizations are therefore not popular in modern multiprocessor designs.

In flat directory schemes, the list of sharers can be included in the directory along with the cache line state. If the directory needs to invalidate a list of sharers the information is available when the original request reaches the home node. Since all relevant directory information is kept in memory at the home node, this approach is known as the *flat memory-based scheme*. Origin 2000 uses this approach; similar designs include the Stanford DASH and Flash machines. There are several possibilities on how to keep the list of sharers. The simplest case is to keep a vector of presence bits where each sharer is represented by a single bit—if the bit is set the corresponding node has a cached copy of the cache line. If the system contains many nodes, the directory information can consume a significant portion of system memory. An alternative to the bit vector scheme is to keep the sharers organized as a linked list (limited pointer directories) or to keep a coarse bit

vector where a single bit represents several nodes. Another alternative is to organize the directory itself as a cache. For example, the Origin systems use two directory formats to keep the metadata overhead low: systems up to 32 processors (16 nodes) use a 32-bit directory entry for each 128-byte cache line (a 3% memory overhead); larger systems use a 96-bit directory entry with a 64 presence bits (a 9% overhead) with the protocol reverting to a coarse-grained scheme where each bit represents eight nodes for systems larger than 128 processors (64 nodes). Regardless of the directory organization, the memory-based scheme keeps all information about the sharers at the home node.

An alternative to the memory-based scheme is for the directory entry to contain only a pointer to the node that holds a copy of the cache line. When there are multiple sharers of the cache line, each node holding a copy keeps a pointer to the next sharer. The sharer list is usually organized as a doubly-linked list to reduce the number of transactions required when one of the sharers removes a copy of the cache line. Instead of the main memory, the directory information is distributed along with the copies of the cache line; this approach is known as the *flat cache-based scheme*. The distributed maintenance of the sharers is considerably more difficult than manipulating the presence bits or a linked list stored at the home node. The complexity issues of this design have been alleviated by the publication of a standard for cache-based directory organization and protocol, the IEEE Scalable Coherent Interface (SCI) [17]. Several commercial systems use the SCI protocol (e.g., Sequent NUMA-Q [25], Convex Exemplar [9], and Data General [8]). While the cache-based schemes reduce the memory used for directory data, the additional transactions required to maintain distributed directory state increase the critical path latency. For systems of moderate size, it is not clear whether the reduction in memory offsets the decrease in memory performance.

#### 3.1.3 Performance and Correctness Issues

The directory protocol must maintain the correct states of cache lines while preserving serialization and ordering relationships required by the coherence and consistency requirements. Additionally, the protocol must be free from deadlock, livelock and, if possible, starvation. At the same time, the directory protocol should satisfy two basic performance goals—to reduce the number of network transactions generated for memory requests and to reduce the number of network transactions on the critical path. This section describes some trade-offs for improving protocol performance for flat memory-based directory protocols.

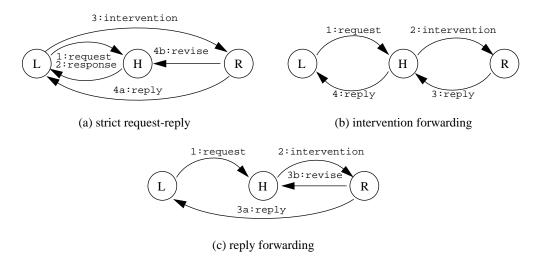

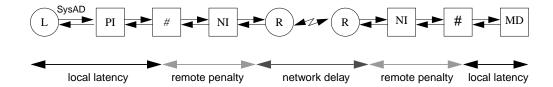

Figure 3.1 shows three different protocol transactions that could be used to move the ownership of a cache line from the current owner R to the requestor L; H is the home node. All three transactions start with the local node sending a request for ownership transfer to the home node. In a *strict request/reply protocol*, the home node responds to the requestor with the identity of the current owner. The local node then sends a separate request to the remote node, which replies to the requestor with the cache line contents and informs the home of the new owner's identity with a revision message. This transaction requires five network messages, four of which are on the critical path.

The number of network messages can be reduced by one when the strict request/reply is replaced by *intervention forwarding*. Instead of the requestor sending the message to the owner, the home node forwards the intervention; the owner responds to the home node, which in turn sends the reply to the requestor. The latency is not reduced as there are still four messages on the critical path. Intervention forwarding has a disadvantage that the home node needs to keep track of

Figure 3.1: Reducing protocol latency through forwarding

outstanding requests instead of the requestor. This means that the buffering resources at the home node have to be increased substantially: if there are P processors in the system, each having up to n outstanding requests, the home node would have to keep track of nP requests in the worst case instead of only n required when the request tracking is done by the requestor. This requirement makes intervention forwarding an unlikely protocol choice.

The number of messages on the critical path can be reduced to three by the use of *reply for-warding*. This transaction is similar to intervention forwarding—the home node forwards the intervention request to the remote owner; however, the remote node sends a reply to the requestor directly and informs the home node with a revision reply. The critical path now consists of the original request message, followed by the intervention and reply; the revision message is sent in parallel with the final reply. This scheme has the best latency and bandwidth characteristics. It does have a disadvantage of increasing the message dependency length from two (request/reply) to three (request/intervention/reply), which has potential implications for deadlock avoidance.

All distributed systems have to consider the possibility of a deadlock. Typical deadlock scenarios in a request/response protocol involve buffer overflow: in order to complete a transaction, a reply message has to be sent to the requestor; if the output queue is full the transaction cannot be completed and the system could end up in a deadlock. One solution for this problem is to provide enough buffer capacity either by anticipating the worst-case scenario or by providing extra buffering in hardware or in main memory (the approach used in the MIT Alewife system [1]). In large systems, providing adequate buffering space could result in underutilization of system resources or could adversely impact system performance. Another solution is to send a negative acknowledge (NACK) whenever there is not enough output buffer space. The third solution is to provide a separate request and reply networks, either by physical network separation or by multiplexing (e.g., virtual channels) with separate buffering space for each channel.

Both the Stanford DASH and the Origin 2000 systems use separate request and reply networks for deadlock avoidance. This solution is adequate for strict request/reply protocols. However, both systems use reply forwarding to minimize request latency. As noted above, reply forwarding extends the dependency chain to request/intervention/reply; in order to prevent a deadlock the

system would have to provide three separate networks. Since the third network would mostly be underutilized, deadlock can be prevented with only two separate networks by detecting when the system could deadlock (e.g., no output buffer space) and either NACK-ing the incoming request (the DASH solution) or reverting to a strict request/reply protocol (Origin 2000). The use of NACKs can lead to the livelock problem: the messages are being exchanged but no forward progress is achieved. In this respect, reverting to strict request/reply protocol is preferable because it does not suffer from livelock problems.

The final issue that the coherence protocol has to consider is starvation. When NACK messages are used there is a possibility some requestors always receive a negative acknowledge while other requestors are accessing a cache line. In reality, starvation is a result of extremely pathological timing. The designers could discard starvation as a remote possibility (e.g., the DASH protocol does nothing to prevent livelock and starvation). A relatively inexpensive solution is to assign priorities to the requests. When a request is NACK-ed the requestor increases the priority and reissues the request. When the home node receives a request it cannot satisfy immediately it updates the priority level which is stored in the directory entry; all requests with priority less than the directory priority are NACK-ed. Eventually, the processor that has been denied access to the cache line will eventually increase priority high enough to override all other processors and obtain the ownership of the cache line.

# 3.2 Origin 2000 Hardware Design

The Origin 2000 architecture is an outgrowth of the Stanford DASH and Flash research projects. The systems debuted in 1996 with machine sizes ranging from two to 64 processors; subsequent versions can scale up to 512 processors. The system is based on MIPS R10000 processors and uses a tightly integrated memory and network controller to implement hardware cache coherence with a flat memory-based directory protocol.

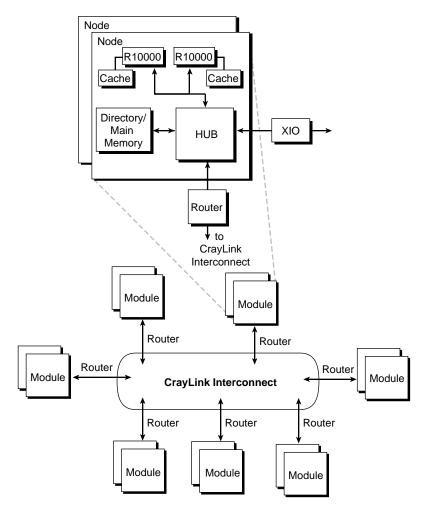

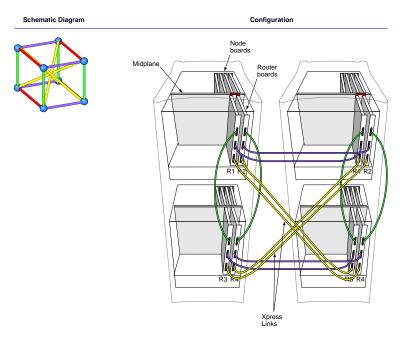

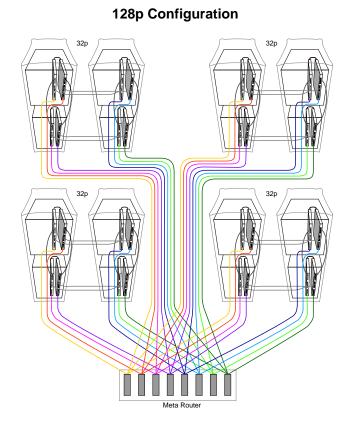

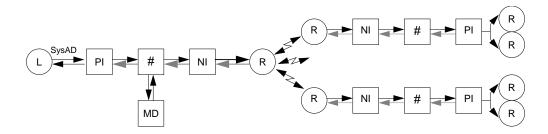

Figure 3.2 shows the logical organization of an Origin 2000 system. It consists of one or more nodes connected with a fast scalable network. Each node contains two R10000 processors, a portion of shared memory, and a directory for cache coherence. The processors are connected to the integrated memory and network controller (the Hub) via a multiplexed system bus (the SysAD bus). The Hub acts as an integrated memory, directory, and network controller and implements a fast I/O port (the XIO interface) connecting the node to the I/O subsystem (the Xbow ASIC). Two nodes access the local I/O subsystem through separate XIO interfaces. The scalable interconnect network is organized as a hypercube. The network is based on a six-ported Router ASIC with two nodes connected to a router and the remaining four ports used for links connected to other Router ASICs. Systems larger than 64 processors are organized as a fat hypercube with individual 32-processor hypercubes connected together with a metarouter.

#### 3.2.1 Cache Coherence Protocol

The Origin 2000 cache coherence protocol is based on the standard three-state invalidation-based directory protocol with several optimizations. It is a nonblocking protocol and it uses reply forwarding with dynamic back-off to prevent deadlocks. The protocol is independent of network

Figure 3.2: Logical organization of the Origin 2000 system

ordering. In addition to processor requests, the protocol supports coherent DMA requests and an innovative way to achieve lazy TLB shootdown.

Each cache line has an unique home determined by the physical address of the cache line. Physical addresses are 40 bits wide: the upper 8 bits select the home node while the lower 32 bits represent the local address within the node. This mode (called M-mode) allows for 256 nodes (512 processors) with a limit of 4 GB of memory per node. An alternative configuration (N-mode) uses 9 bits to select the node and 31 bits for local offset for a total of 512 nodes with 2 GB of memory per node; this mode is not used in existing Origin systems. An in-depth description of global addressing in the Origin systems is given in [49, pp. 3–23].

The directory protocol is nonblocking: the home node will not buffer a request if the response cannot be generated immediately (e.g., because the line is owned by another processor). Rather than buffering the request at home, the directory state is changed to a transient (busy) state while the current owner is being tracked down. The current owner responds to the intervention by updating the directory with a revision message, which causes the transient state to change to one of the permanent states (unowned, shared or exclusive). Requests to cache lines in busy state are

acknowledged immediately with a negative response, which causes the requestor to reissue the request later. Starvation is prevented by assigning requests a priority value, which is a function of the number of times the request was denied.

The protocol does not rely on network ordering: messages could take different routes through the interconnect network and arrive at the destination out of order. The out-of-order message delivery can result in several race conditions. Rather than imposing strict network ordering on the interconnect, the Origin directory protocol handles race conditions explicitly. The only messages which require point-to-point network ordering are certain uncached operations used to implement programmed I/O (PIO).

#### **Directory States**

The directory protocol is based on states given in Table 3.1. Four of the states are stable: in the unowned state, the memory keeps the only copy of the cache line; in the shared state, the cache line may be replicated read-only in one or more processor's caches (the identity of sharers is kept in a bit vector stored in the directory); in the exclusive state, one processor or I/O unit keeps an exclusive copy of the cache line that is either clean or dirty (again, the identity of the owner is stored in the directory); in the poisoned state, the cache line has migrated to another node during a page migration and the access will cause a trap if a processor attempts to access this line through a stale TLB mapping. Transient states are used in the intermediate stages of protocol transactions: busy shared and exclusive states indicate that the directory should not handle a new request for the cache line until the previous transaction has completed; the wait state is used to prevent a writeback race condition.

| state                  | description                                       |

|------------------------|---------------------------------------------------|

| unowned (UOWN)         | No cached copies in the system                    |

| poisoned (POIS)        | Not cached, access returns bus error              |

| shared (SHRD)          | Read-only copies cached by one or more nodes      |

| exclusive (EXCL)       | Cached in exclusive state by one processor or I/O |

| busy shared (BUSYS)    | Directory is busy tracking down a shared copy     |

| busy exclusive (BUSYE) | Directory is busy tracking down an exclusive copy |

| waiting (WAIT)         | Directory is waiting for a revision message       |

Table 3.1: Directory states in the Origin directory protocol

The directory information is kept separate from the main memory so that memory and directory operations can be overlapped. In addition to the cache line state, the directory keeps the identity of the owner for exclusive lines and a list of sharers for shared lines. The sharers are kept in a bit vector where each bit represents a node; invalidation messages thus target both processors on the node. The decision to keep sharers on a per-node basis allows a 64-bit presence bit vector to cover all nodes in a 128-processor system. Larger systems use a different mode to keep track of the sharers. If all sharers are located in the same 64-node *octant* the presence bits again represent one node in the octant; invalidations are sent to individual nodes. When the sharers are spread across octants, the directory uses a coarse bit vector scheme where each bit represents eight nodes.

Invalidations are sent to all eight nodes, even if some of these nodes may not have a cached copy of the cache line.

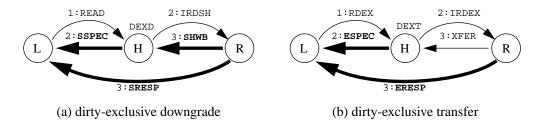

#### **Protocol Optimizations**

The first optimization that aims to improve protocol performance is the use of *speculative replies*. For all requests that require a data response, the directory controller always performs directory lookup and memory read in parallel. In most cases, the data are sent as part of the response (e.g., read requests on unowned or shared lines). When the home node is not the current owner of the cache line, the data are sent to the requestor in a speculative reply. The speculative data are used if the current owner has a clean copy of the cache line. By using speculative replies, the protocol assumes that it is not likely that the owner has modified its copy. If this is not the case the updated data have to be returned with the response from the current owner while the speculative data are discarded.

The Origin protocol supports the full MESI protocol used by the R10000 processor to manage the L2 cache, including the clean-exclusive state. In exclusive state, the processor is the exclusive owner of the cache line but it has not modified it yet. The processor can invalidate an exclusive line from its cache at any time; this does not present a problem on a snoopy bus because snoop request will miss in owner's cache when another processor requests a line. This does present a problem in a directory protocol—while the processor has silently dropped the cache line the home node still keeps the processor as the owner. One solution is to extend the protocol with replacement hints: whenever the processor drops a clean line it sends a revision message to the home node. The disadvantage of this approach is that it uses extra network traffic and wastes directory bandwidth. The Origin protocol allows a processor to drop a clean line from its cache without notifying the home node (silent clean-exclusive replacement). If the same processor later requests the cache line again the directory assumes that the processor has dropped the cache line and immediately returns a fresh copy. On the other hand, if another processor requests a copy the home node forwards the intervention request to the owner as if it still had a copy in its cache. The intervention request will fail. However, the requesting processor can use data returned in the speculative reply. In this case, the extra cost is the additional intervention request, which would not be necessary if the protocol used replacement hints. On the other hand, silent dropping of exclusive lines is beneficial to uniprocessor applications because directory bandwidth is not wasted with replacement hints.

In order to support application execution in ccNUMA environment, the Origin designers decided to implement page migration to improve application performance [7]. Efficient page migration requires a fast data copy mechanism and the ability to globally purge stale TLB entries. Implementing a global TLB shootdown algorithm without hardware support can be very costly. Origin directory protocol allows for an efficient global TLB purge by supporting *directory poisoning*. A cache line can be "poisoned" during the data-copy phase by the copy engine. The poison read request invalidates all cached copies of the line and sets its directory state to poisoned. When a processor attempts to read a poisoned cache line via a stale TLB mapping the directory returns an error. This in turn invokes the kernel exception handler, which recognizes the special error and invalidates the stale TLB entry. No expensive global synchronization operations are necessary: processors invalidate stale TLB entries on demand.

#### **Protocol Transactions**

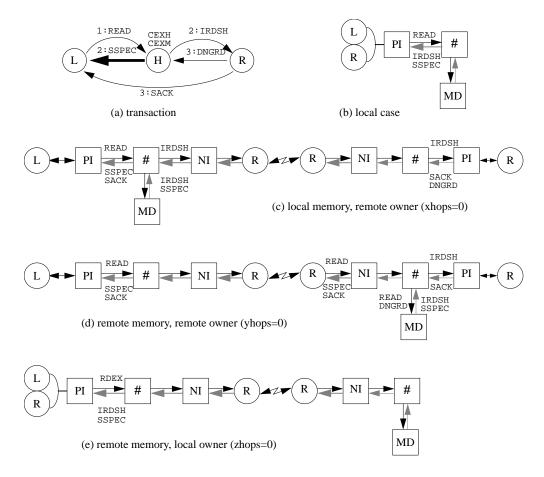

The directory protocol supports coherent processor read and write operations, coherent I/O requests which are used by the DMA engines, and a number of noncoherent operations which are used for processor-initiated programmed I/O. The processor can generate three types of read requests to coherent memory. The *read-shared request* (RDSH) asks for a read-only copy of the data; this request is used for instruction fetches. The *read request* (READ) returns an exclusive copy if there are no shared copies cached in the system; an exclusive copy is downgraded to a shared state with both the requestor and the current owner in the list of sharers; if the line is already shared the requestor is simply added to the list of sharers. This request is generated when a load instruction misses in the cache. The *read-exclusive request* (RDEX) asks for an exclusive copy of the cache line; it is generated when a store instruction misses in the cache.

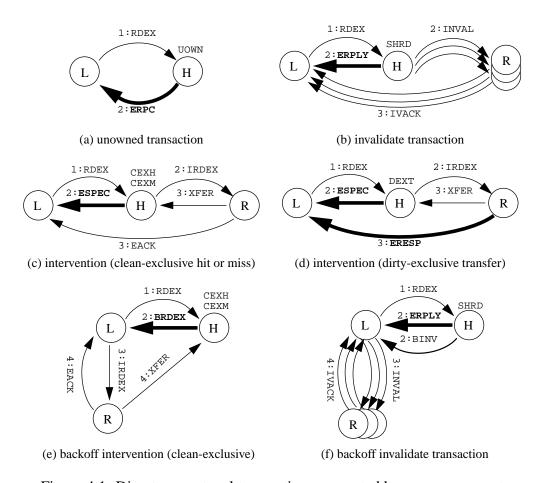

Depending on the state of the cache line, read requests trigger different types of directory transactions. If the line is in the unowned state, the home node sends the reply immediately and updates the directory to reflect the new owner. The unowned transaction requires only two messages, a request and a reply. If the line is shared read-only among several nodes in the system, and a processor requests an exclusive copy of the cache line, the shared copies have to be invalidated before the requestor can assume exclusive ownership. The resulting invalidate transaction is a three-step transaction: the requestor sends a request to the home node, the home node forwards invalidations to the sharers, and the sharers reply with acknowledgment messages to the requestor. Finally, if a processor requests a copy of a cache line whose directory state indicates that another processor holds a valid copy, the remote processor needs to relinquish the ownership and possibly send a locally modified copy to the requestor. There are several variants of this scenario which involve three participants: the requestor, the home node and the remote owner. The intervention transacton is a broad term, covering all variants of this scenario. The Origin directory protocol supports two more transaction types, variants of the intervention and invalidate transactions, which are used when the system detects a possibility of a deadlock. In this case, the directory protocol reverts to a strict request/reply protocol. The resulting backoff intervention and backoff invalidate transactions are four-step transactions where the local node first sends a request to the home node, the home responds with a backoff response to the requestor, the local node then sends the intervention or invalidate requests to the remote nodes and waits for the response.

#### 3.2.2 Node Board

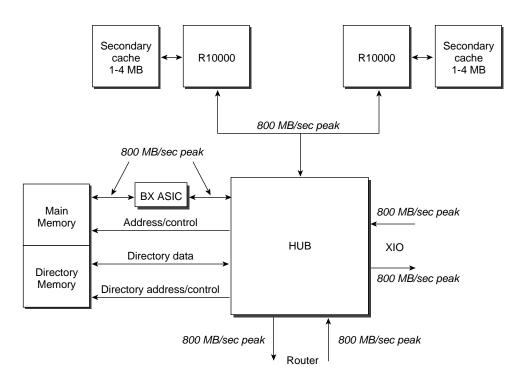

The node board is the basic building block of the Origin system. It holds two R10000/R12000 processors and a portion of system memory and the associated directory memory. Two bidirectional interfaces connect the node board to the rest of the system. The communication with other nodes goes through the CrayLink port which connects the node to a router board. The local I/O system is accessible through the XIO port. At the center of the node board is the Hub ASIC, which connects the processors, memory, I/O and network interfaces.

Figure 3.3 shows the block diagram of the node board. The processors communicate with the Hub over a shared SysAD bus. Each processor has a separate L2 integrated instruction and data cache. Rather than implementing a snoopy cluster, the two processors use the SysAD bus as a shared resource and do not perform snoops on it. This reduces the latency because the Hub does not have to wait for the result of a snoop before forwarding the request to memory; however, it is not

Figure 3.3: Block diagram of the node board

possible to perform local cache-to-cache transfers. There are separate dual inline memory modules (DIMMs) for main and directory memory which makes it possible for the Hub memory/directory interface performs data and directory lookups in parallel. The BX ASIC is used to multiplex the memory data path in order to save Hub pins.

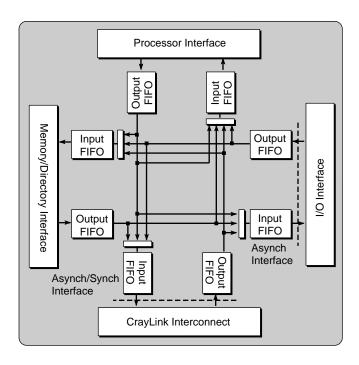

The Hub is internally divided into four separate interfaces. Internal messages are used to communicate between the Hub interfaces and each interface has a separate input and output queues. The central crossbar connects the four interfaces together. Figure 3.4 shows the block diagram of the Hub ASIC. The external connections (CrayLink and XIO ports) both use a similar protocol; the only difference is in the messages used by the communication protocol. The CrayLink messages are tailored for the needs of directory-based cache coherence whereas the messages in the XIO protocol are used to control the I/O devices (storage, network and graphics) which have different requirements. The original version of the Origin featured R10000 processors running at 195 MHz; in these systems, the Hub core operates at 97.5 MHz. Newer systems with 250 MHz R10000 processors and 300 or 400 MHz R12000 processors have the Hub running at 100 MHz. All Origin systems have the interconnect network and the XIO interface running at 400 MHz. To accommodate the variations in Hub frequency, both the network and the XIO interface have to provide an asynchronous interface.

One of the Hubs in the system can be designated as the source of a global clock. The clock information is propagated by the routers to all other nodes in the system. This hardware feature is used to implement a global, synchronous high-resolution (800 ns) cycle counter. Applications can map a page of Hub physical space into their address space to access the cycle counter directly, which results in an extremely low access time (300 ns).

Figure 3.4: Block diagram of the Hub ASIC

#### Memory/Directory Interface

The memory/directory (MD) interface is an integrated memory and directory controller: it processes memory requests generated by the processors and I/O controllers in the system and maintains directory information for the memory on the node board.